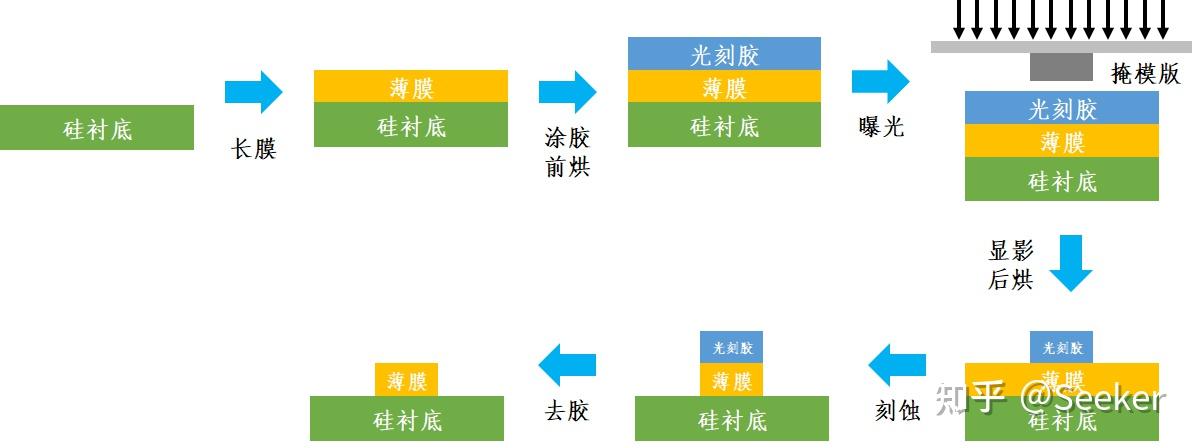

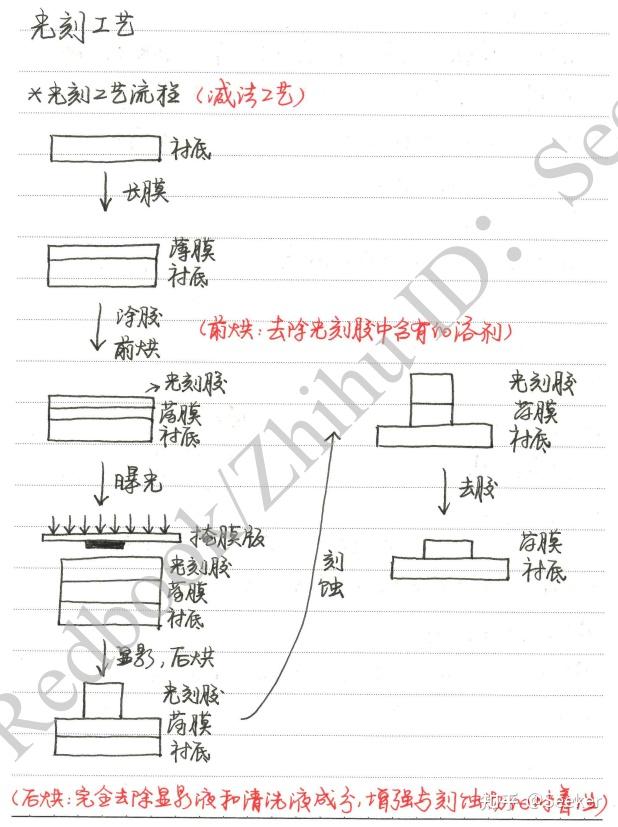

一、光刻工艺流程

光刻工艺

二、曝光

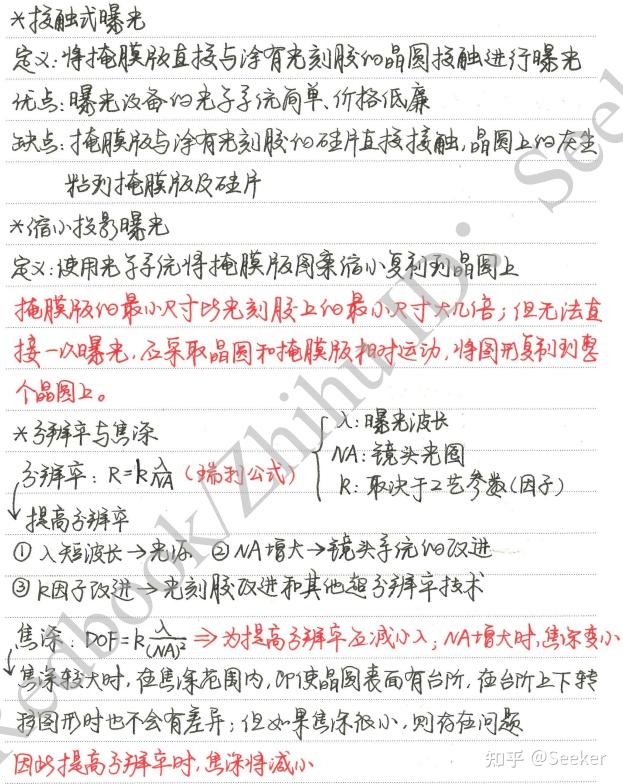

1、接触式曝光

定义:将掩模版直接与涂有光刻胶的晶圆接触进行曝光

优点:曝光设备的光学系统简单、价格低廉

缺点:掩模版与涂有光刻胶的硅片直接接触,晶圆上的灰尘粘到掩模版及硅片

2、缩小投影曝光

定义:使用光学系统将掩模版图案缩小到复制到晶圆上(多次曝光)

3、分辨率(Resolution)

λ是曝光光源波长,NA是投影透镜的数值孔径,k是工艺参数因子

提高分辨率的方法:① 使用λ较短的光源;② 对镜头系统进行改进,增大NA;③ 对光刻工艺进行改进,提升k因子

4、聚焦深度(DOF)

聚焦深度较大时,在焦深范围内,即使晶圆表面有台阶,在台阶上下转移图形时也不会有差异。

减小λ,增大NA时,DOF变小,因此如果提高分辨率,聚焦深度将会变小,这是具有矛盾性的。

5、曝光光源历史

G-line 436nm→I-line 365nm→KrF 248nm→ArF 193nm→ArF浸液→ArF浸液+DP(两次图形)→EUV

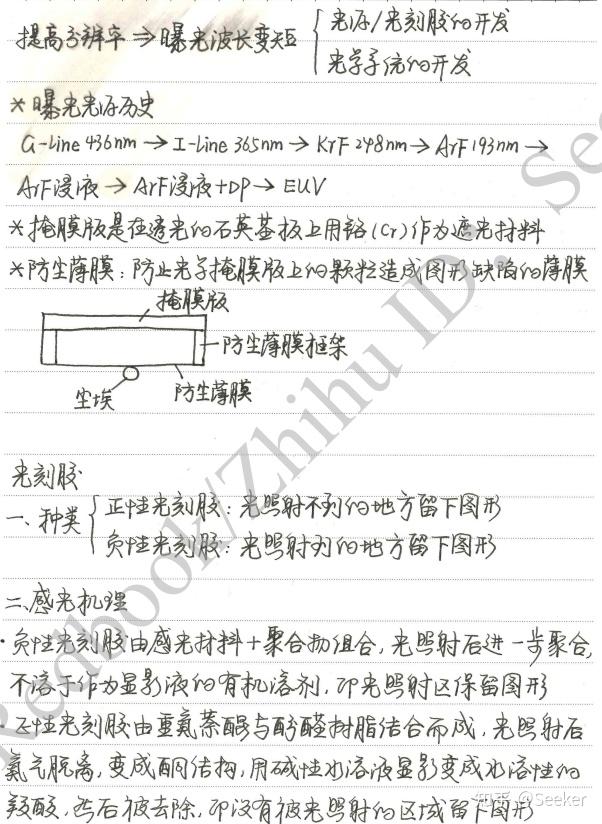

三、光刻胶

1、分类

正性光刻胶:光照射不到的地方留下图形

负性光刻胶:光照射到的地方留下图形

2、感光机理

正性光刻胶由重氮萘醌与酚醛树脂结合而成,光照射后氮气脱离,变成酮结构,用碱性水溶液显影变成水溶性羧酸,然后被去除,没有被光照射的区域留下图形。

负性光刻胶由感光材料+聚合物组合,光照射后进一步聚合,不溶于作为显影液的有机溶剂,即光照射区域保留图形。

注:负性光刻胶发生的是聚合反应,在分辨率方面处于劣势,在先进工艺中常用正性光刻胶

3、要求

中短波长段的可见光可使得光刻胶感光,因此光刻区域与普通洁净室是隔离开的,采用不会使光刻胶感光的照明光源,工作时称为黄光区。

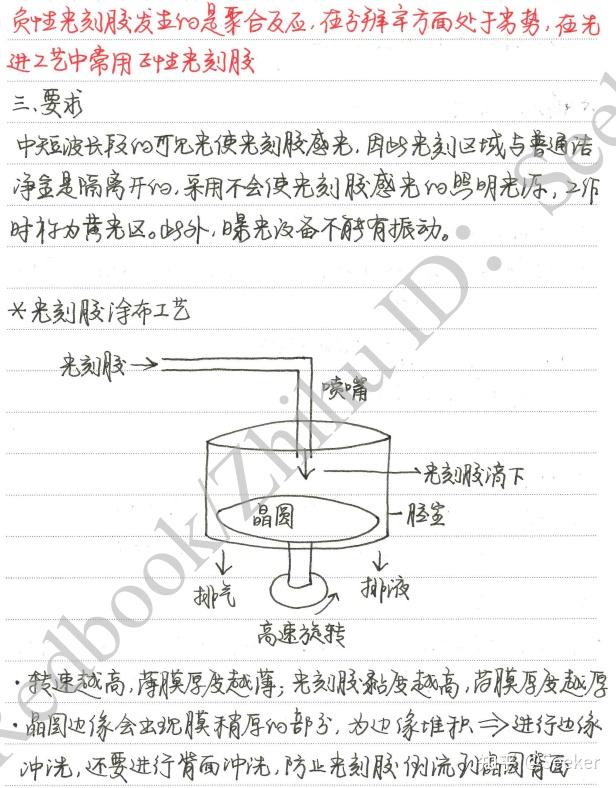

4、涂布工艺

转速越高,薄膜厚度越薄;光刻胶黏度越高,薄膜厚度越厚。

晶圆边缘会出现膜稍厚的部分,为边缘堆积→边缘冲洗时,还要进行背面冲洗,防止光刻胶倒流到晶圆背面。

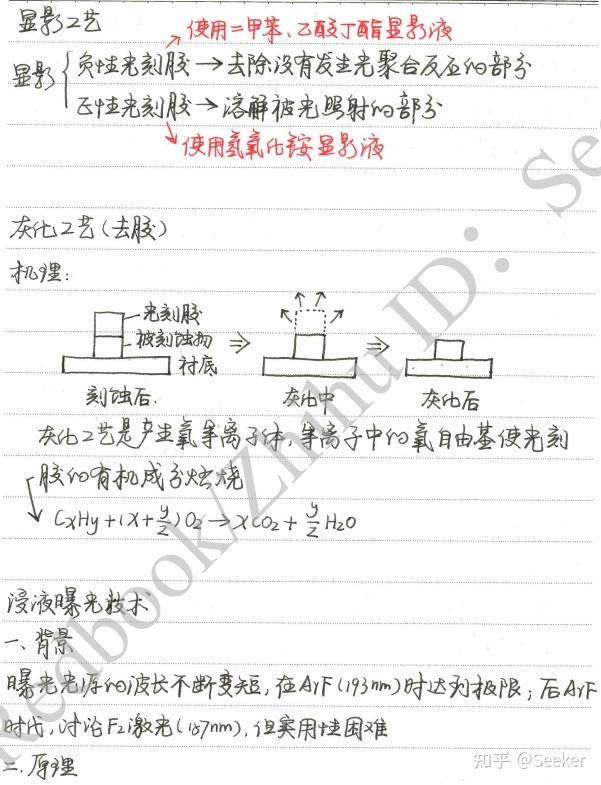

四、显影工艺

正性光刻胶→使用氢氧化铵显影液溶解被光照射的部分

负性光刻胶→使用二甲苯、乙酸丁酯显影液去除没有发生光聚合反应的部分

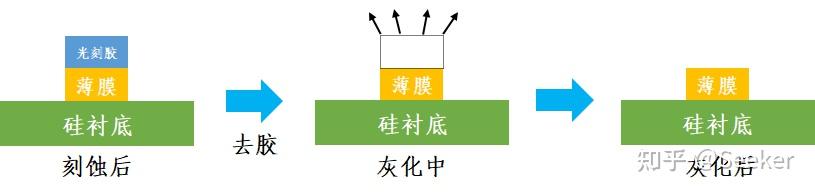

五、灰化(去胶)工艺

机理:灰化工艺是产生氧等离子体,等离子体中的氧自由基使光刻胶的有机成分燃烧

灰化(去胶)工艺

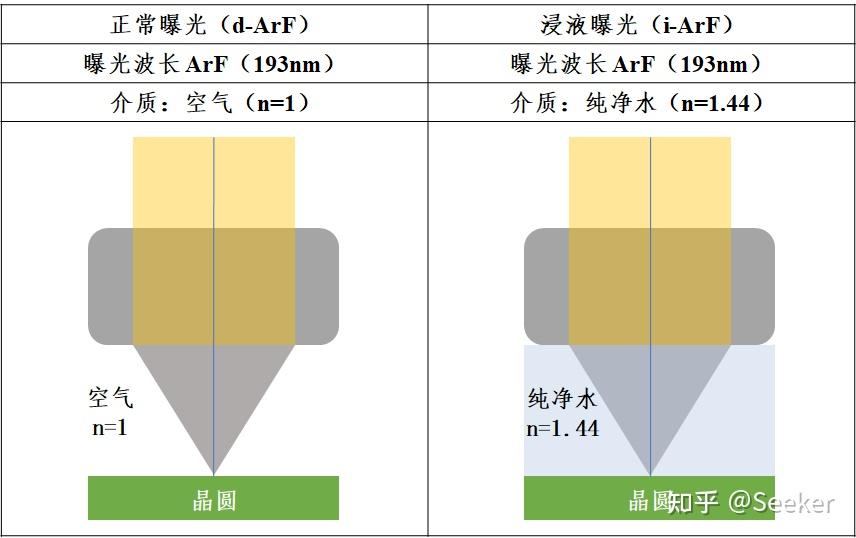

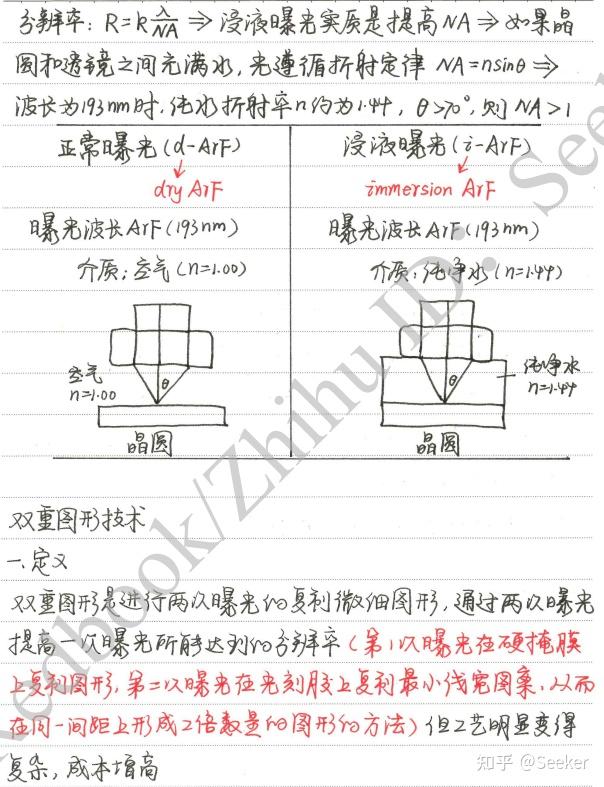

六、浸液曝光技术

1、背景

曝光光源的波长不断变短,在ArF(193nm)时达到极限;后ArF时代,讨论F2激光(157nm),但实用性困难。

2、原理

浸液曝光实质是提高NA。在晶圆和透镜之间充满水,光遵循折射定律NA=n·sinθ,波长为193nm时,纯水折射率n约为1.44,θ>70°,则NA>1。

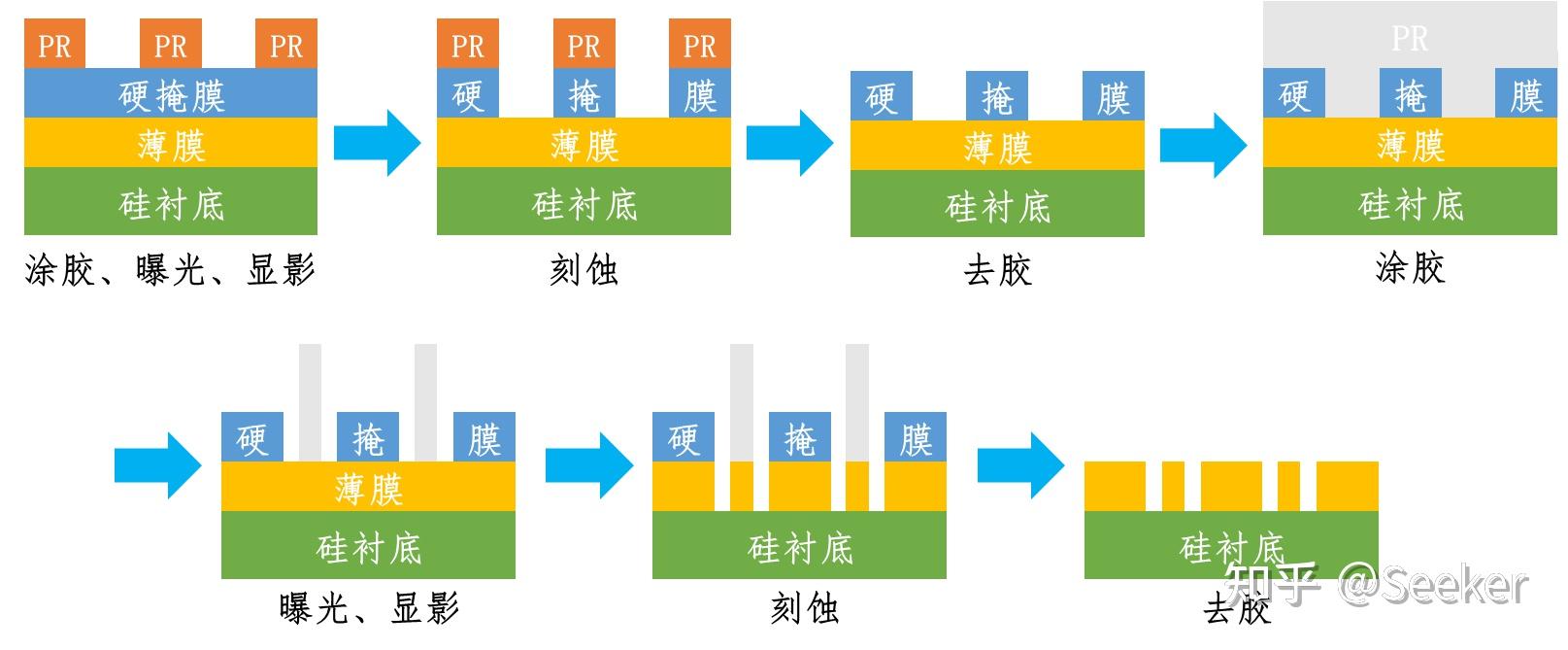

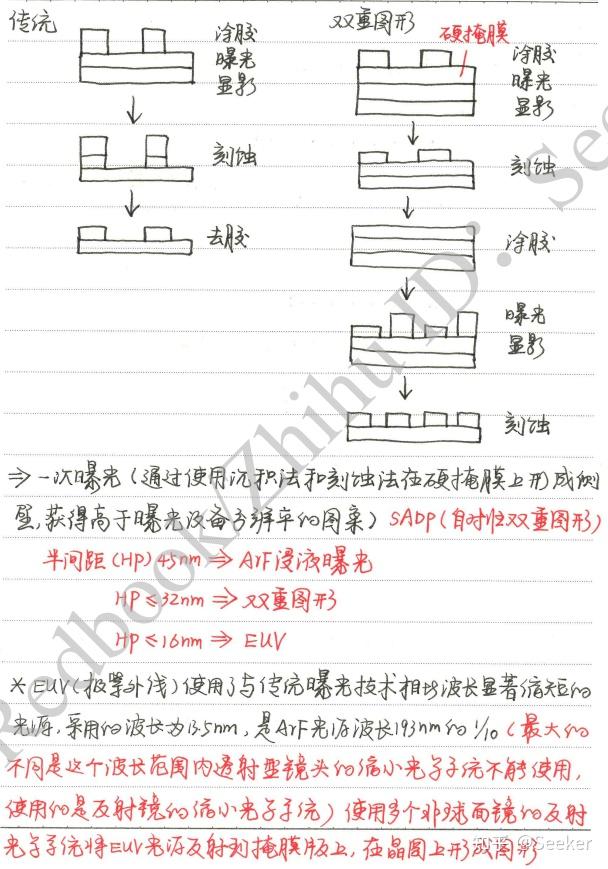

七、双重图形技术

1、定义

双重图形是进行两次曝光的复制微细图形的技术,通过两次曝光来提高一次曝光所能达到的分辨率(第一次曝光是在硬掩膜上复制图形,第二次曝光是在光刻胶上复制最小线宽图案,从而在同一间距上形成2倍数量的图形的方法),但工艺明显变复杂,成本增加。

双重图形曝光技术

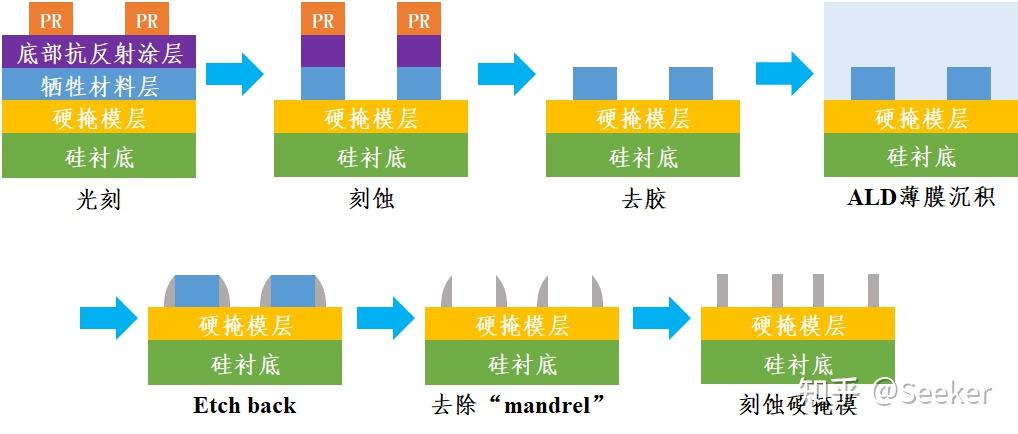

2、自对准双重成像技术 SADP

自对准双重成像技术(self-aligned double patterning, SADP),思路是在一次光刻完成后,相继使用非光刻工艺步骤(薄膜沉积、刻蚀等)实现对光刻图形的空间倍频,最后使用另外一次光刻和刻蚀把多余的图形去掉。

工艺流程:在衬底表面沉积一层牺牲材料(sacrifice layer)(CVD材料)→进行光刻和刻蚀,将掩模上的图形转移到牺牲材料层上,牺牲材料层上的图形称为mandrel或core→使用原子层沉积技术(ALD)在mandrel的表面和侧面沉积一层厚度相对比较均匀的薄膜(spacer材料)→使用RIE工艺将沉积的spacer材料再刻蚀掉,称为etch back [由于mandrel侧壁的几何效应,沉积在图形两侧的材料会残留下来,形成spacer,使用选择性强的腐蚀液把mandrel去掉,留下spacer在衬底表面,spacer图形的周期是光刻图形的一半,实现了空间图形密度的倍增]→使用RIE工艺把spacer图形转移到衬底里的硬掩模上[侧壁成像工艺(sidewall imaging process,SIP)]

自对准双重成像技术 SADP

3、EUV

极紫外线(EUV)使用与传统曝光技术相比波长显著缩短的光源(13.5nm)

最大的不同是这个波长范围内透射型镜头的缩小光学系统不能使用,使用的是反射镜的缩小光学系统,使用多个非球面镜的反射光学系统将EUV光源反射到掩模版上,在晶圆在形成图形。

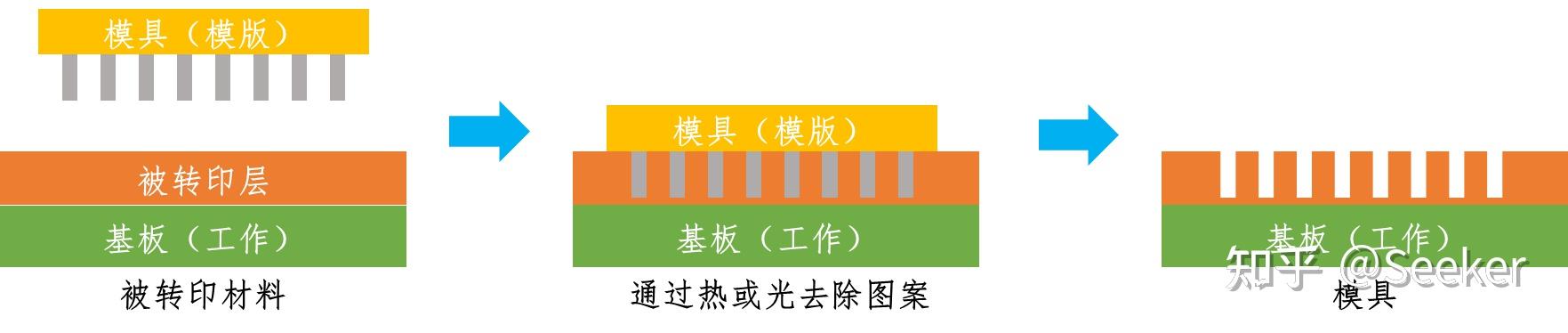

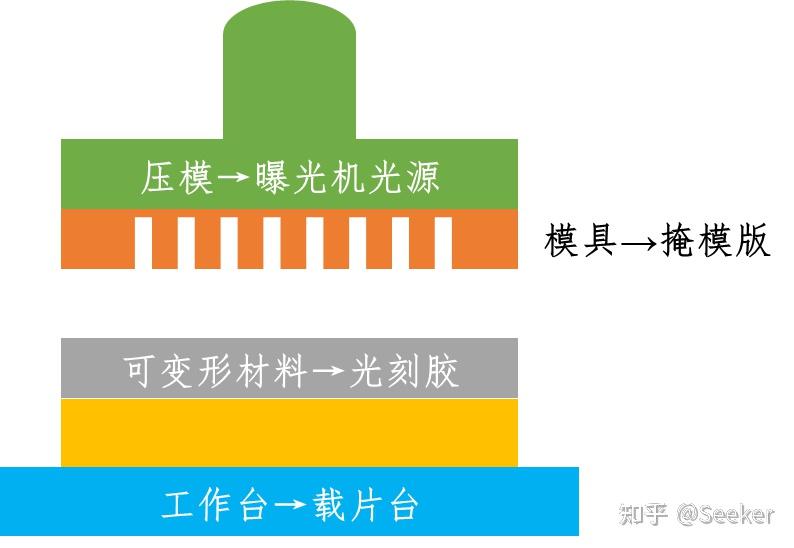

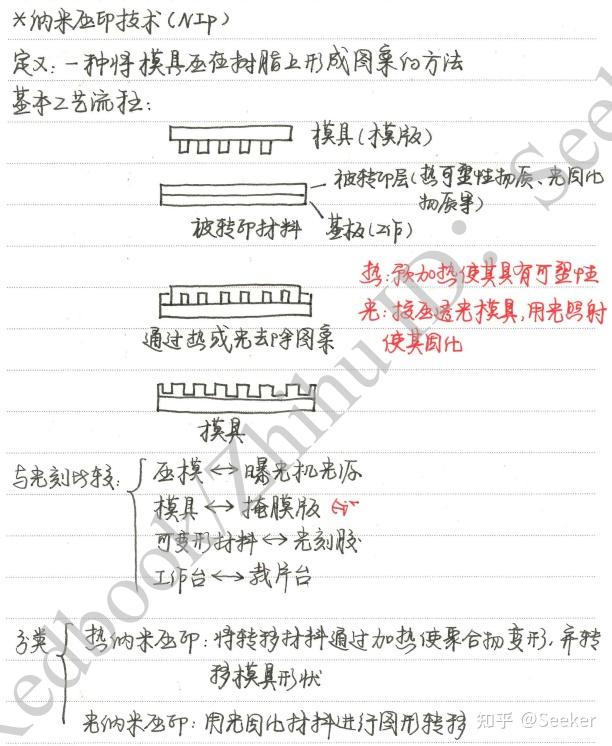

八、纳米压印技术(NIP)

1、定义

一种将模具压在树脂上形成图案的方法

2、工艺流程

热:预加热使其具有可塑性

光:按压透光模具,用光照射使其固化

3、分类

热纳米压印:将转移材料通过加热使聚合物变形,并转移模具形状

光纳米压印:用光固化材料进行图形转移

<hr/>可关注我索要完整版半导体制造工艺pdf手写笔记。

|