华为Mate 60 Pro搭载的麒麟9000S处理器,引起了公众对国产芯片制造水平的关注。这颗处理器采用了7nm工艺,而且是在中国大陆生产的。这是怎么做到的呢?

要制造7nm工艺的芯片,一般需要使用EUV(极紫外)光刻机,因为它的光源波长只有13.5nm,可以在晶圆上刻出更细微的图案。但是,EUV光刻机是由荷兰ASML公司垄断生产的,而且受到美国等国家的出口管制,中国无法获得。

目前,中国能够自主生产的光刻机只有DUV(深紫外)光刻机,它的光源波长为193nm,远大于7nm。按理说,DUV光刻机无法制造出7nm工艺的芯片,但是华为却做到了。

那么,华为是如何用DUV光刻机制造出7nm工艺芯片的呢?这里涉及到一些芯片制造的技术细节和窍门,我将从以下几个方面来介绍:

什么是光刻?

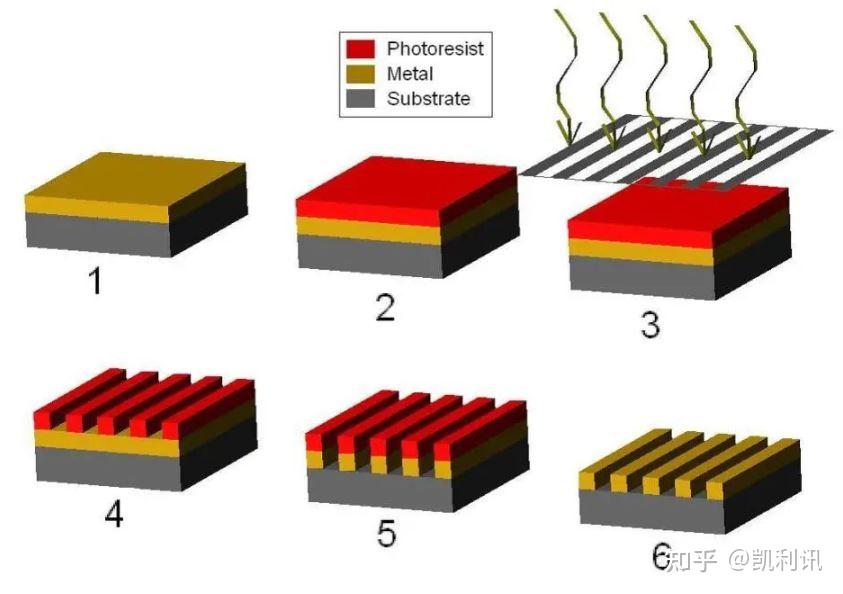

光刻是芯片制造过程中最重要也最复杂的一个步骤,它的作用是将电路图案转移到晶圆表面上。我们可以把它比作电影放映:电影胶片上有图像信息,通过投影仪将图像放大投射到银幕上;而光刻则是将掩膜版上有电路信息,通过光刻机将电路缩小投射到晶圆上。

光刻机是如何工作的?

- 准备掩膜版和晶圆。掩膜版相当于电影胶片,是用金属铬在特殊玻璃上刻出的模板。晶圆相当于银幕,是用硅或其他半导体材料制成的圆形薄片,表面涂有感光材料——光刻胶。

- 将掩膜版放在光刻机里,用紫外光照射掩膜版。掩膜版上有铬镀层的部分会遮挡紫外光,没有铬镀层的部分会透过紫外光。这样就形成了一个图案化的紫外光束,它会经过一系列的透镜和反射镜,最终缩小投射到晶圆上。

- 晶圆上的光刻胶会被紫外光照射后发生化学变化,变得易于溶解。用化学溶液将变化的光刻胶清洗掉后,就露出了晶圆表面。这样就在晶圆上形成了一个与掩膜版相同的电路图案。

- 用其他的工艺方法,在晶圆上刻蚀、沉积、扩散等,制造出晶体管、金属互连线等芯片结构。重复这样的过程,就可以一层一层地叠加出一个完整的芯片。

- 要制造出更小尺寸的晶体管,就需要缩短紫外光的波长,这样才能在晶圆上刻出更精细的电路图案。

工艺节点是什么意思?

芯片制造商通常用工艺节点来标识自己的芯片加工技术水平,比如7nm、14nm、28nm等等。这些数字原本是指晶体管的尺寸,比如7nm就是指晶体管的栅极长度为7nm。

但是随着技术的发展,这些数字已经失去了实际的物理意义,只是一种市场营销的手段。现在的7nm工艺芯片上的晶体管尺寸都远大于7nm,“7nm”只是一个“标签”,并不代表真正的物理尺寸。

DUV光刻机如何制造7nm工艺芯片?

我们知道,DUV光刻机的光源波长为193nm,远大于7nm。如果直接用DUV光刻机在晶圆上刻出7nm的图案,是不可能做到的。

华为是如何用DUV光刻机制造出7nm工艺芯片?

华为并没有直接用DUV光刻机在晶圆上刻出7nm的图案,而是用了一些“魔法”技术,在DUV光刻机上进行了多次复杂的操作,最终实现了类似于EUV光刻机的效果。 这些“魔法”技术包括:

- 多重曝光:即用多个掩膜版,在同一块晶圆上进行多次光刻操作,将不同的图案叠加在一起,形成更细微的图案。这相当于用多个胶片拼接出一个更精细的图像。

- 自对准双图案化(SADP):即先用一个掩膜版,在晶圆上刻出一个较粗糙的图案,然后在图案上覆盖一层硬质材料(如氧化硅),再用另一个掩膜版,在硬质材料上刻出一个较细致的图案。最后去掉硬质材料和多余的部分,只留下最终想要的图案。这相当于用两个胶片分别放大和缩小一个图像,再将它们重合在一起。

- 自对准四图案化(SAQP):即在SADP的基础上再进行一次类似的操作,从而将图案进一步细分。这相当于用四个胶片分别放大和缩小两个图像,再将它们重合在一起,形成一个更复杂的图像。这样就可以在DUV光刻机上实现类似于EUV光刻机的效果,制造出更小尺寸的电路图案。

为了让DUV能制造出7nm工艺芯片,业界已经竭尽全力,使用了多重曝光、自对准双图案化、自对准四图案化等“魔法”技术,但这也带来了巨大的复杂度和成本。如果继续采用DUV制造5nm工艺芯片,四重曝光也不够了,需要6-8重曝光,以及更多的掩膜版,更长的光刻时间,更高的物力成本,这已经超出了业界的承受范围。

所以5nm芯片出来时,刚好EUV光刻机也准备好了,才将业界从繁琐的多重曝光下解脱出来,而7nm工艺也成为目前业界使用DUV制造出来的最后一代工艺。

华为麒麟9000S就是在这样的背景下诞生的一颗奇迹之芯。它不仅是国产手机上首款7nm工艺芯片,而且是在中国大陆生产的。它展示了国产芯片制造水平的飞跃和自主创新能力的提升。它也为国产手机带来了更强大的性能和更低的功耗。它是国产手机突破7nm芯片制造难关的最佳证明,也是国产手机走向世界舞台的一张亮丽名片。 |